2021

Sultana, Nik; Sonchack, John; Giesen, Hans; Pedisich, Isaac; Han, Zhaoyang; Shyamkumar, Nishanth; Burad, Shivani; DeHon, André; Loo, Boon Thau

Flightplan: Dataplane Disaggregation and Placement for P4 Programs Proceedings Article

In: 18th USENIX Symposium on Networked Systems Design and Implementation (NSDI 21), pp. 571–592, USENIX Association, 2021, ISBN: 978-1-939133-21-2.

@inproceedings{Sultana2021,

title = {Flightplan: Dataplane Disaggregation and Placement for P4 Programs},

author = {Nik Sultana and John Sonchack and Hans Giesen and Isaac Pedisich and Zhaoyang Han and Nishanth Shyamkumar and Shivani Burad and André DeHon and Boon Thau Loo},

url = {https://www.usenix.org/conference/nsdi21/presentation/sultana},

isbn = {978-1-939133-21-2},

year = {2021},

date = {2021-04-01},

booktitle = {18th USENIX Symposium on Networked Systems Design and Implementation (NSDI 21)},

pages = {571–592},

publisher = {USENIX Association},

keywords = {},

pubstate = {published},

tppubtype = {inproceedings}

}

DeHon, André; Giesen, Hans; Sultana, Nik; Xiao, Yuanlong

Meta-level issues in Offloading: Scoping, Composition, Development, and their Automation Journal Article

In: arXiv preprint arXiv:2104.01929, 2021.

@article{dehon2021meta,

title = {Meta-level issues in Offloading: Scoping, Composition, Development, and their Automation},

author = {André DeHon and Hans Giesen and Nik Sultana and Yuanlong Xiao},

year = {2021},

date = {2021-01-01},

journal = {arXiv preprint arXiv:2104.01929},

keywords = {},

pubstate = {published},

tppubtype = {article}

}

2019

Xiao, Yuanlong; Park, Dongjoon; Butt, Andrew; Giesen, Hans; Han, Zhaoyang; Ding, Rui; Magnezi, Nevo; Rubin, Raphael; DeHon, Andre

Reducing FPGA Compile Time with Separate Compilation for FPGA Building Blocks Proceedings Article

In: 2019 International Conference on Field-Programmable Technology (ICFPT), pp. 153-161, 2019.

@inproceedings{Xiao2019,

title = {Reducing FPGA Compile Time with Separate Compilation for FPGA Building Blocks},

author = {Yuanlong Xiao and Dongjoon Park and Andrew Butt and Hans Giesen and Zhaoyang Han and Rui Ding and Nevo Magnezi and Raphael Rubin and Andre DeHon},

doi = {10.1109/ICFPT47387.2019.00026},

year = {2019},

date = {2019-01-01},

booktitle = {2019 International Conference on Field-Programmable Technology (ICFPT)},

pages = {153-161},

keywords = {},

pubstate = {published},

tppubtype = {inproceedings}

}

2018

Giesen, Hans; Shi, Lei; Sonchack, John; Chelluri, Anirudh; Prabhu, Nishanth; Sultana, Nik; Kant, Latha; McAuley, Anthony J; Poylisher, Alexander; DeHon, André; Loo, Boon Thau

In-network Computing to the Rescue of Faulty Links Proceedings Article

In: Proceedings of the 2018 Morning Workshop on In-Network Computing, pp. 1–6, ACM, Budapest, Hungary, 2018, ISBN: 978-1-4503-5908-5.

@inproceedings{Giesen:2018:ICR:3229591.3229595,

title = {In-network Computing to the Rescue of Faulty Links},

author = {Hans Giesen and Lei Shi and John Sonchack and Anirudh Chelluri and Nishanth Prabhu and Nik Sultana and Latha Kant and Anthony J McAuley and Alexander Poylisher and André DeHon and Boon Thau Loo},

url = {http://doi.acm.org/10.1145/3229591.3229595},

doi = {10.1145/3229591.3229595},

isbn = {978-1-4503-5908-5},

year = {2018},

date = {2018-01-01},

booktitle = {Proceedings of the 2018 Morning Workshop on In-Network Computing},

pages = {1--6},

publisher = {ACM},

address = {Budapest, Hungary},

series = {NetCompute '18},

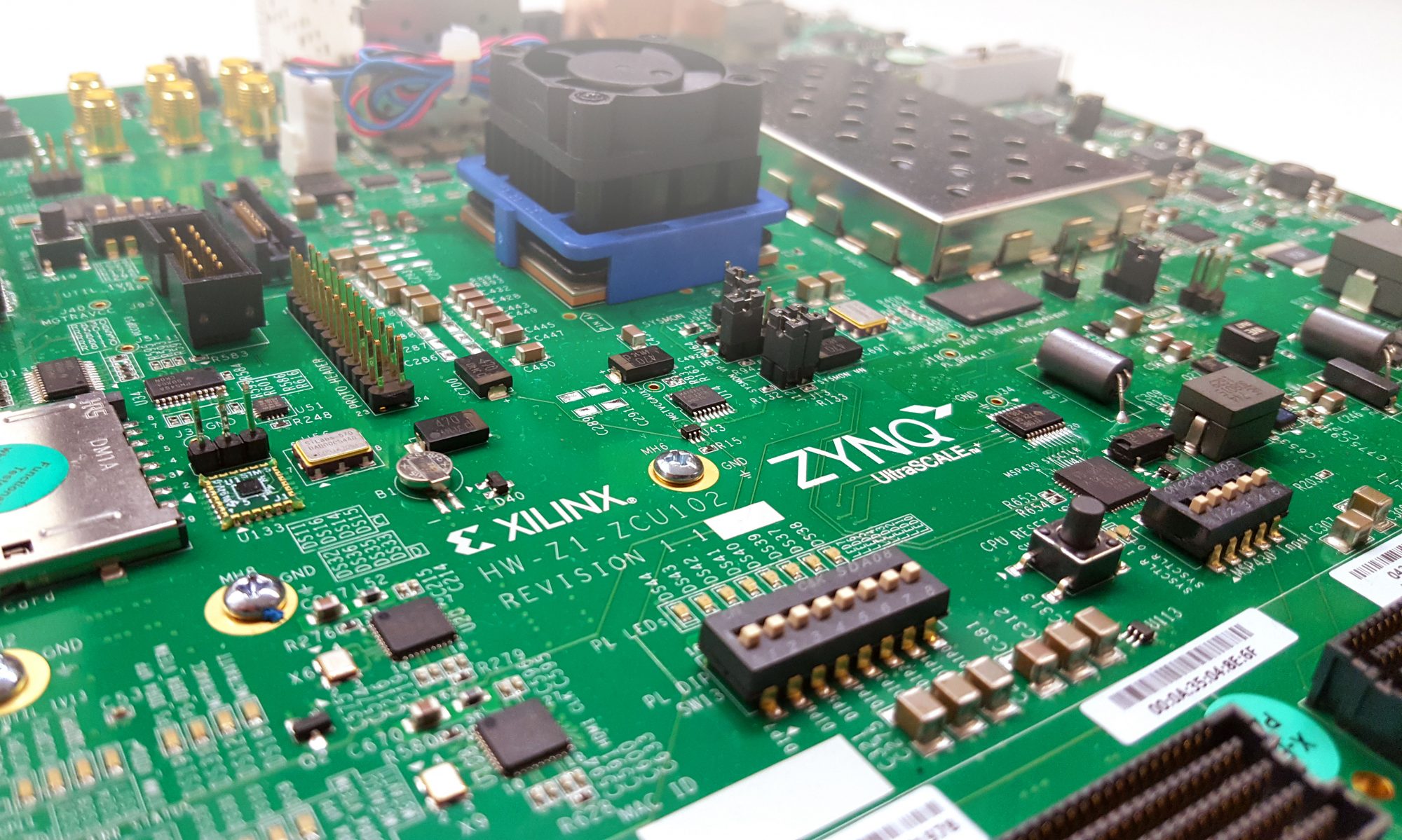

abstract = {Failing network links are usually disabled, and packets are routed around them until the links are repaired. While it is often possible to utilize some of a failing link's capacity, losing what remains of a link's capacity is typically deemed preferable to the erratic effect that unreliable links can have on application-level behavior.

We describe a new network function that relies on in-network computing to limit the erratic effect of failing network links, to enable the continued use of those links until they can be repaired. We explore the design space using ns-3, and evaluate our implementation on a physical test-bed that includes programmable switches and reconfigurable hardware. Our current hardware prototype can almost saturate a 10GbE link while using around 10% of our FPGA's resources.},

keywords = {},

pubstate = {published},

tppubtype = {inproceedings}

}

We describe a new network function that relies on in-network computing to limit the erratic effect of failing network links, to enable the continued use of those links until they can be repaired. We explore the design space using ns-3, and evaluate our implementation on a physical test-bed that includes programmable switches and reconfigurable hardware. Our current hardware prototype can almost saturate a 10GbE link while using around 10% of our FPGA's resources.

Giesen, Hans; Gojman, Benjamin; Rubin, Raphael; Kim, Ji; Dehon, André

Continuous Online Self-Monitoring Introspection Circuitry for Timing Repair by Incremental Partial-Reconfiguration (COSMIC TRIP) Journal Article

In: ACM Trans. Reconfigurable Technol. Syst., vol. 11, no. 1, pp. 3:1–3:23, 2018, ISSN: 1936-7406.

@article{Giesen:2018:COS:3178391.3158229,

title = {Continuous Online Self-Monitoring Introspection Circuitry for Timing Repair by Incremental Partial-Reconfiguration (COSMIC TRIP)},

author = {Hans Giesen and Benjamin Gojman and Raphael Rubin and Ji Kim and André Dehon},

url = {http://doi.acm.org/10.1145/3158229},

doi = {10.1145/3158229},

issn = {1936-7406},

year = {2018},

date = {2018-01-01},

journal = {ACM Trans. Reconfigurable Technol. Syst.},

volume = {11},

number = {1},

pages = {3:1--3:23},

publisher = {ACM},

address = {New York, NY, USA},

abstract = {We show that continuously monitoring on-chip delays at the LUT-to-LUT link level during operation allows a field-programmable gate array to detect and self-adapt to aging and environmental timing effects. Using a lightweight (<4% added area) mechanism for monitoring transition timing, a Difference Detector with First-Fail Latch, we can estimate the timing margin on circuits and identify the individual links that have degraded and whose delay is determining the worst-case circuit delay. Combined with Choose-Your-own-Adventure precomputed, fine-grained repair alternatives, we introduce a strategy for rapid, in-system incremental repair of links with degraded timing. We show that these techniques allow us to respond to a single aging event in less than 190ms for the toronto20 benchmarks. The result is a step toward systems where adaptive reconfiguration on the time-scale of seconds is viable and beneficial.},

keywords = {},

pubstate = {published},

tppubtype = {article}

}

2017

Giesen, H; Rubin, R; Gojman, B; DeHon, A

Self-Adaptive Timing Repair Journal Article

In: IEEE Design Test, vol. 34, no. 6, pp. 54-62, 2017, ISSN: 2168-2356.

@article{8031029,

title = {Self-Adaptive Timing Repair},

author = {H Giesen and R Rubin and B Gojman and A DeHon},

doi = {10.1109/MDAT.2017.2750912},

issn = {2168-2356},

year = {2017},

date = {2017-12-01},

journal = {IEEE Design Test},

volume = {34},

number = {6},

pages = {54-62},

abstract = {This article describes a method to continuously monitor paths delays in an operational FPGA design and to improve slow paths by incremental partial reconfiguration. Since online delay measuring is more accurate than design time estimation, this approach allows to balance delays which can be used to improve performance or reduce power consumption. In addition, it counteracts aging effects and prolongs the system’s useful life time. —Axel Jantsch, TU Wien},

keywords = {},

pubstate = {published},

tppubtype = {article}

}

Giesen, Hans; Rubin, Raphael; Gojman, Benjamin; DeHon, André

Quality-Time Tradeoffs in Component-Specific Mapping: How to Train Your Dynamically Reconfigurable Array of Gates with Outrageous Network-delays Proceedings Article

In: Proceedings of the 2017 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, pp. 85–94, ACM, Monterey, California, USA, 2017, ISBN: 978-1-4503-4354-1.

@inproceedings{Giesen:2017:QTC:3020078.3026124,

title = {Quality-Time Tradeoffs in Component-Specific Mapping: How to Train Your Dynamically Reconfigurable Array of Gates with Outrageous Network-delays},

author = {Hans Giesen and Raphael Rubin and Benjamin Gojman and André DeHon},

url = {http://doi.acm.org/10.1145/3020078.3026124},

doi = {10.1145/3020078.3026124},

isbn = {978-1-4503-4354-1},

year = {2017},

date = {2017-01-01},

booktitle = {Proceedings of the 2017 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays},

pages = {85--94},

publisher = {ACM},

address = {Monterey, California, USA},

series = {FPGA '17},

abstract = {How should we perform component-specific adaptation for FPGAs? Prior work has demonstrated that the negative effects of variation can be largely mitigated using complete knowledge of device characteristics and full per-FPGA CAD flow. However, the cost of per-FPGA characterization and mapping could be prohibitively expensive. We explore light-weight options for per-FPGA mapping that avoid the need for a priori device characterization and perform less expensive per FPGA customization work. We characterize the tradeoff between Quality-of-Results (energy, delay) and per-device mapping costs for 7 design points ranging from complete mapping based on knowledge to no per-device mapping. We show that it is possible to get 48-77% of the component-specific mapping delay benefit or 57% of the energy benefit with a mapping that takes less than 20 seconds per FPGA. An incremental solution can start execution after a 21 ms bitstream load and converge to 77% delay benefit after 18 seconds of runtime.},

keywords = {},

pubstate = {published},

tppubtype = {inproceedings}

}

2016

Giesen, H; Gojman, B; Rubin, R; Kim, J; DeHon, A

Continuous Online Self-Monitoring Introspection Circuitry for Timing Repair by Incremental Partial-Reconfiguration (COSMIC TRIP) Proceedings Article

In: 2016 IEEE 24th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), pp. 111-118, 2016.

@inproceedings{7544759,

title = {Continuous Online Self-Monitoring Introspection Circuitry for Timing Repair by Incremental Partial-Reconfiguration (COSMIC TRIP)},

author = {H Giesen and B Gojman and R Rubin and J Kim and A DeHon},

doi = {10.1109/FCCM.2016.36},

year = {2016},

date = {2016-05-01},

booktitle = {2016 IEEE 24th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM)},

pages = {111-118},

abstract = {We show that continuously monitoring on-chip delays at the LUT-to-LUT link level during operation allows an FPGA to detect and self-adapt to aging and environmental effects on timing. Using a lightweight (<;4% added area) mechanism for monitoring transition timing, a Difference Detector with First-Fail Latch, we can estimate the timing margin on circuits and identify the individual links that have degraded and whose delay is determining the worst-case circuit delay. Combined with Choose-Your-own-Adventure precomputed, fine-grained repair alternatives, we introduce a strategy for rapid, in-system incremental repair of links with degraded timing. We show that these techniques allow us to respond to a single aging event in less than 300 ms for the toronto20 benchmarks. The result is a step toward systems where adaptive reconfiguration on the time-scale of seconds is viable and beneficial.},

keywords = {},

pubstate = {published},

tppubtype = {inproceedings}

}

2015

Bachmann, C; Vidojkovic, M; Huang, X; Lont, M; Liu, Y; Ding, M; Busze, B; Gloudemans, J; Giesen, H; Sbai, A; van Schaik, G; Kiyani, N; Kanda, K; Oishi, K; Masui, S; Philips, K; de Groot, H

A 3.5mW 315/400MHz IEEE802.15.6/proprietary mode digitally-tunable radio SoC with integrated digital baseband and MAC processor in 40nm CMOS Proceedings Article

In: 2015 Symposium on VLSI Circuits (VLSI Circuits), pp. C94-C95, 2015, ISSN: 2158-5601.

@inproceedings{7231336,

title = {A 3.5mW 315/400MHz IEEE802.15.6/proprietary mode digitally-tunable radio SoC with integrated digital baseband and MAC processor in 40nm CMOS},

author = {C Bachmann and M Vidojkovic and X Huang and M Lont and Y Liu and M Ding and B Busze and J Gloudemans and H Giesen and A Sbai and G van Schaik and N Kiyani and K Kanda and K Oishi and S Masui and K Philips and H de Groot},

doi = {10.1109/VLSIC.2015.7231336},

issn = {2158-5601},

year = {2015},

date = {2015-06-01},

booktitle = {2015 Symposium on VLSI Circuits (VLSI Circuits)},

pages = {C94-C95},

abstract = {An energy-efficient, flexible radio SoC with RF front-end (RFFE), digital baseband (DBB) and microcontroller (MCU) for medical/healthcare applications in 315/400 MHz bands is presented. The SoC is fully-compliant with the IEEE 802.15.6 standard in 400MHz bands, and also supports proprietary modes, including high data rate (HDR) modes with x2/4/8 data rates (max 3.6Mb/s) to support applications like EEG, and low-power modes with 1/16 data rate to minimize sensor node power consumption. The total power consumption of 3.5mW (RX, 3.6Mb/s, -77dBm sensitivity) enables best-in-class power efficiency of 1nJ/bit.},

keywords = {},

pubstate = {published},

tppubtype = {inproceedings}

}

Liu, Y; Bachmann, C; Wang, X; Zhang, Y; Ba, A; Busze, B; Ding, M; Harpe, P; van Schaik, G; Selimis, G; Giesen, H; Gloudemans, J; Sbai, A; Huang, L; Kato, H; Dolmans, G; Philips, K; de Groot, H

13.2 A 3.7mW-RX 4.4mW-TX fully integrated Bluetooth Low-Energy/IEEE802.15.4/proprietary SoC with an ADPLL-based fast frequency offset compensation in 40nm CMOS Proceedings Article

In: 2015 IEEE International Solid-State Circuits Conference - (ISSCC) Digest of Technical Papers, pp. 1-3, 2015, ISSN: 0193-6530.

@inproceedings{7063013,

title = {13.2 A 3.7mW-RX 4.4mW-TX fully integrated Bluetooth Low-Energy/IEEE802.15.4/proprietary SoC with an ADPLL-based fast frequency offset compensation in 40nm CMOS},

author = {Y Liu and C Bachmann and X Wang and Y Zhang and A Ba and B Busze and M Ding and P Harpe and G van Schaik and G Selimis and H Giesen and J Gloudemans and A Sbai and L Huang and H Kato and G Dolmans and K Philips and H de Groot},

doi = {10.1109/ISSCC.2015.7063013},

issn = {0193-6530},

year = {2015},

date = {2015-02-01},

booktitle = {2015 IEEE International Solid-State Circuits Conference - (ISSCC) Digest of Technical Papers},

pages = {1-3},

abstract = {This paper presents an ultra-low-power (ULP) fully-integrated Bluetooth Low-Energy(BLE)/IEEE802.15.4/proprietary RF SoC for Internet-of-Things applications. Ubiquitous wireless sensors connected through cellular devices are becoming widely used in everyday life. A ULP RF transceiver is one of the most critical components that enables these emerging applications, as it can consume up to 90% of total battery energy. Furthermore, a low-cost radio design with an area-efficient fully integrated RF SoC is an important catalyst for developing such applications. By employing a low-voltage digital-intensive architecture, the presented SoC is fully compliant with BLE and IEEE802.15.4 PHY/Data-link requirements and achieves state-of-the-art power consumption of 3.7mW for RX and 4.4mW for TX.},

keywords = {},

pubstate = {published},

tppubtype = {inproceedings}

}