Following are some examples of projects that I worked on to showcase my skills.

HLS tuner

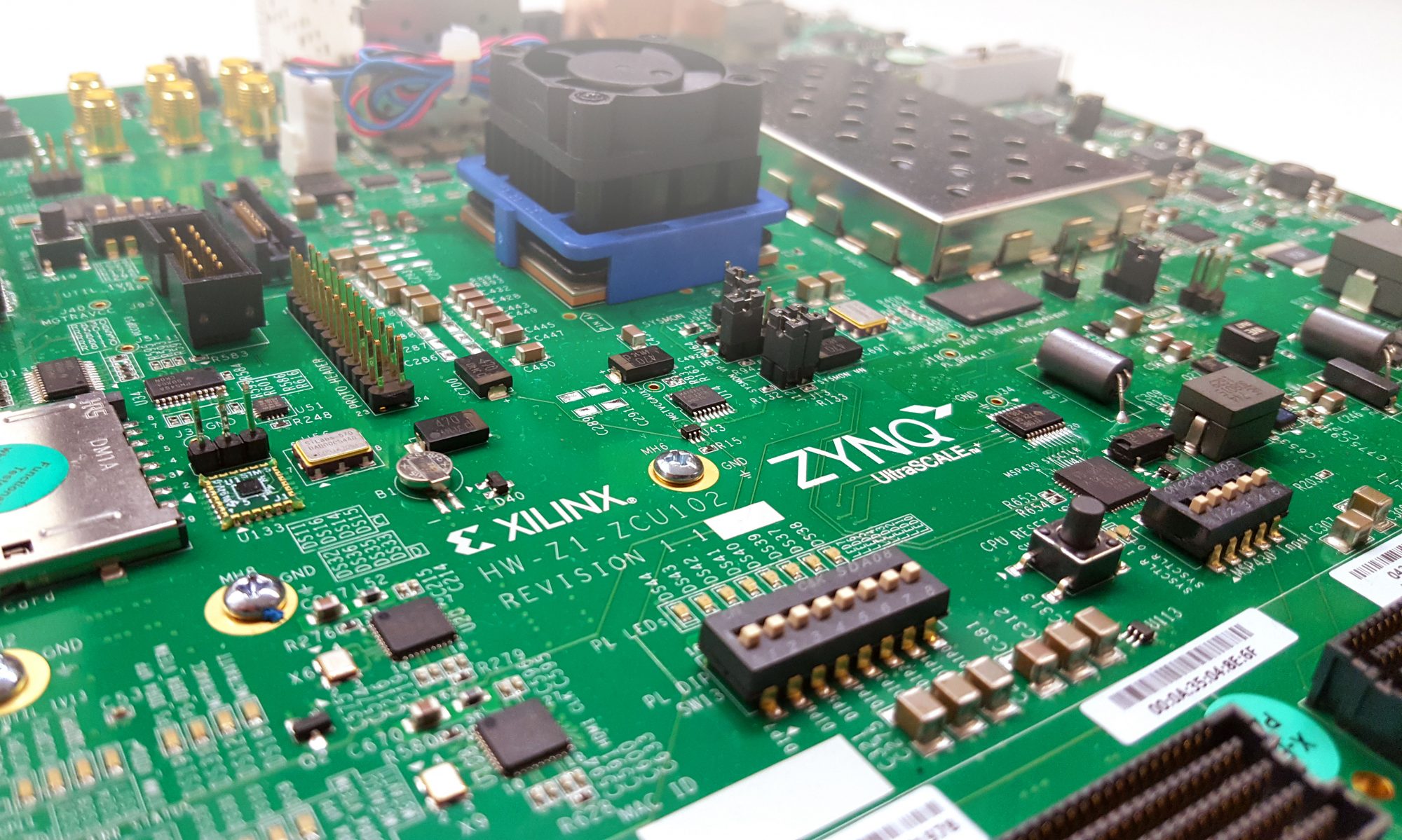

This is a design space exploration tool for high-level synthesis (HLS) kernels that I developed at Xilinx. It demonstrates my Python and machine-learning skills.

Error correction booster

As part of the FlightPlan project, I created an in-network accelerator for Reed-Solomon Erasure (RSE) error correction. The accelerator was written in C/C++ for HLS, which communicates via input and output buffers written in RTL (VHDL) with an Ethernet IP block.

Deduplication project

I wrote this C++ code when I was the teaching assistant of the ESE-5320 course at the University of Pennsylania. The goal of the project was to build an FPGA accelerator to compress and decompress a stream of data. This code was meant as a starting point for the student.

Verilog parser

I wrote this Python code as a coding assignment part of an application procedure to a semiconductor company.